IntelliMagic Vision release 10.1.0 expands the Connectivity Topology View to the area of LPARs.

In a z/OS sysplex decisions made during the LPAR configuration process influence the physical processor share that each logical processor has. Having an optimal processor configuration will result in optimizing processor and cache usage. More work will be done with fewer processor cycles. Optimizing the processor and cache usage is important for optimizing the CPU costs. IntelliMagic Vision’s Topology Viewer will help the z/OS systems manager with this task.

Topology Viewer

IntelliMagic Vision release 9.25.0 introduced the Topology Viewer for Disk Configuration Connectivity in July 2020. Now IntelliMagic Vision release 10.1.0 expands the Topology Viewer capabilities to the area of LPAR Topology. PR/SM dynamically assigns logical CPs on each LPAR to hardware chips, nodes, and drawers, seeking to optimize cache efficiency. This LPAR topology can have a very significant impact on processor CPU efficiency. Remote cache accesses can take hundreds of machine cycles. SMF 99.14 records are produced every 5 minutes and capture drawer/node/chip location data for each logical CP. The new visualization of LPAR Topology data makes this data far easier to analyze and interpret.

Example of IntelliMagic Vision’s LPAR Topology View

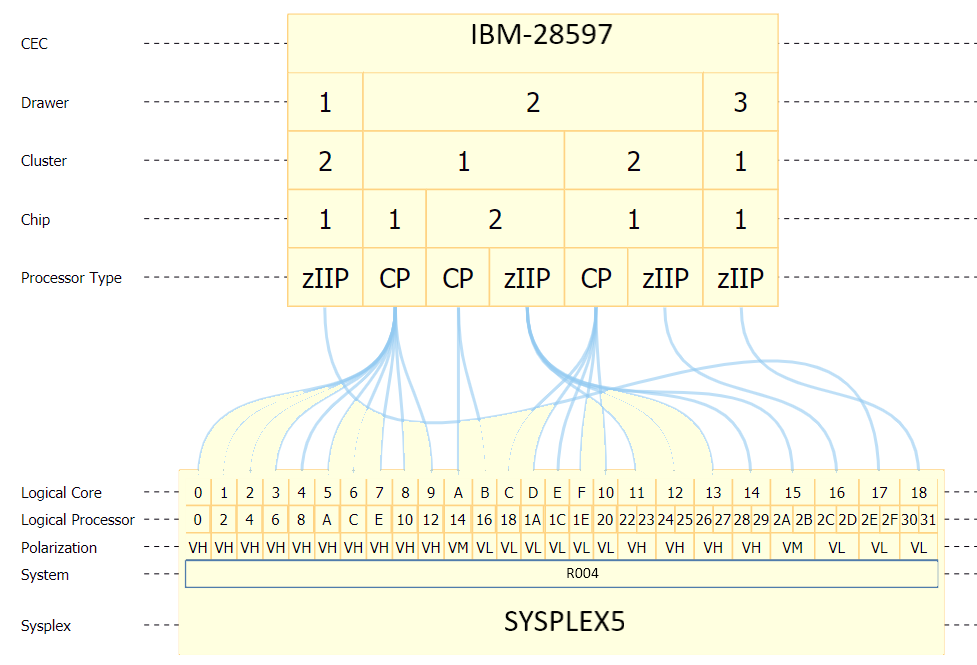

IntelliMagic Vision will initially show a complete topology diagram (see image below). This contains all logical CPs defined to this LPAR. It combines physical resources beginning from the CEC with logical resources beginning from the sysplex. The LPAR Topology View certainly contains a lot of important information. In this form it is easy to understand.

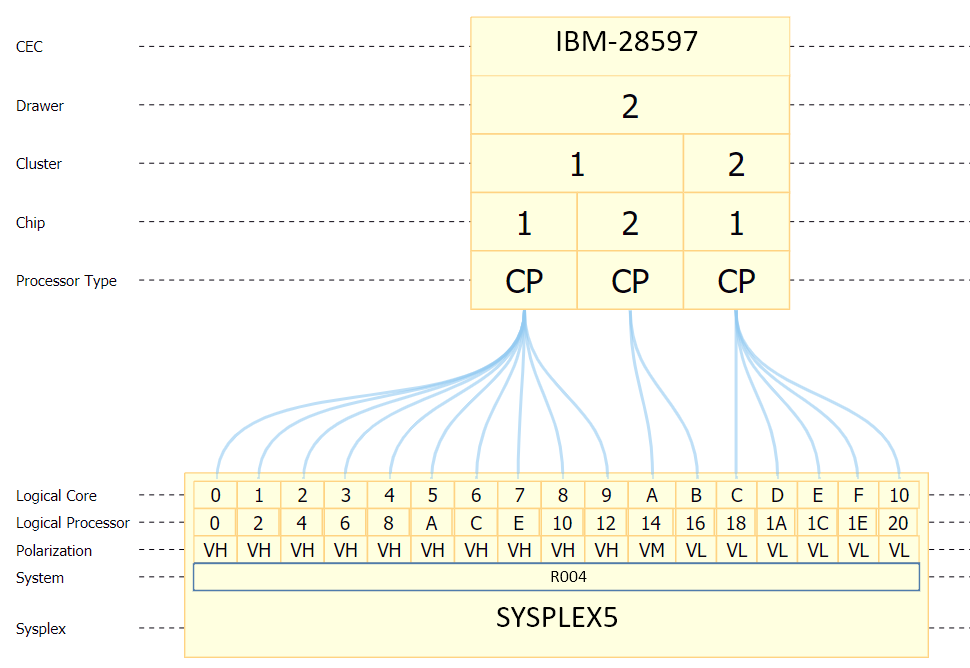

The primary focus of processor cache analysis is typically on general purpose CPs. That CPU generates the software expense. A common way to use this view shown above is to select any CP and drilldown. The “CP only” view pictured below makes it immediately apparent that all the Vertical High logical CPs for this LPAR are colocated on a single physical chip. This is the ideal situation for processor cache efficiency.

When looking at the LPAR topology, it is important to realize that the processor assignments may change frequently. The topology may well be different during the peak day online time frame compared to the evening batch time frame.

For more information see also John Ticic’s blog.

You May Also Be Interested In:

What's New with IntelliMagic Vision for z/OS? 2024.2

February 26, 2024 | This month we've introduced changes to the presentation of Db2, CICS, and MQ variables from rates to counts, updates to Key Processor Configuration, and the inclusion of new report sets for CICS Transaction Event Counts.

Why Am I Still Seeing zIIP Eligible Work?

zIIP-eligible CPU consumption that overflows onto general purpose CPs (GCPs) – known as “zIIP crossover” - is a key focal point for software cost savings. However, despite your meticulous efforts, it is possible that zIIP crossover work is still consuming GCP cycles unnecessarily.

Top ‘IntelliMagic zAcademy’ Webinars of 2023

View the top rated mainframe performance webinars of 2023 covering insights on the z16, overcoming skills gap challenges, understanding z/OS configuration, and more!