We all know that our z/OS LPARs rely on processors to execute the code to run our business. These processors may be general purpose or specialty processors (e.g. zIIP). We also need to plan on having sufficient resources available for our workload when we design our LPARs.

Processor Topology – What Is It?

During our LPAR design stage, we look at the workload, set appropriate LPAR weights, and specify the number of logical processors, and type, that are required.

For an LPAR managed by HiperDispatch, this process results in logical processors being defined that will be dispatched onto physical processors. When an LPAR dispatches work, it will typically choose the next available logical processor. PR/SM on the other hand will dispatch the logical processor onto a physical processor based on the weights that have been set. This is referred to as “Vertical CPU Management”.

The LPAR processors will have different logical processor shares. Some of these processors may have a 100% share which means that the work will be dispatched to the same physical processor. We refer to these as Vertical High polarity processors. Others will have lower processor shares and will result in sharing a physical processor. These processors are referred to as Vertical Medium or Vertical Low polarity processors. In addition, Vertical Low processors may be parked or unparked (i.e. unused).

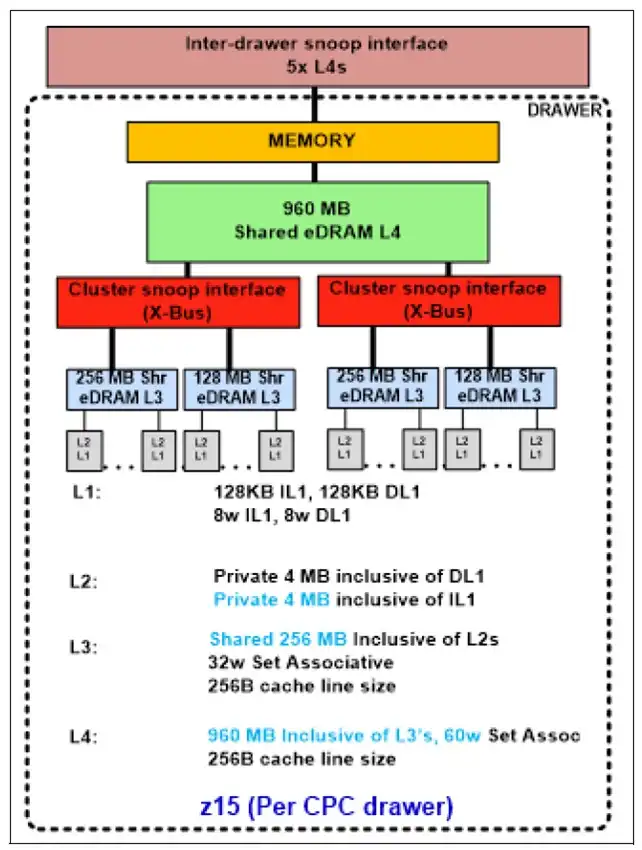

Physical processors rely on different levels of cache to obtain instructions and data necessary to execute the workload. This differs between zSeries hardware processor generations and is referred to as the processor topology.

Using a z15 as an example, the topology consists of processors residing on chips. These chips contain different levels of cache and are contained in clusters that are subsequently contained in drawers. Note: These terms are specific to each zSeries hardware generation.

Figure 1: z15 Cache Structure

LPAR Topology – How To View It?

In IntelliMagic Vision, we support processing the SMF 99 subtype 14 HiperDispatch records. These records contain important processor information and should be gathered on each LPAR. In addition, there are other recommended SMF records so that we can have a complete picture. RMF/CMF generate CPU records (SMF 70 subtype 1) and the Hardware Instrumentation Services (HIS) process generates hardware capacity statistics (SMF 113).

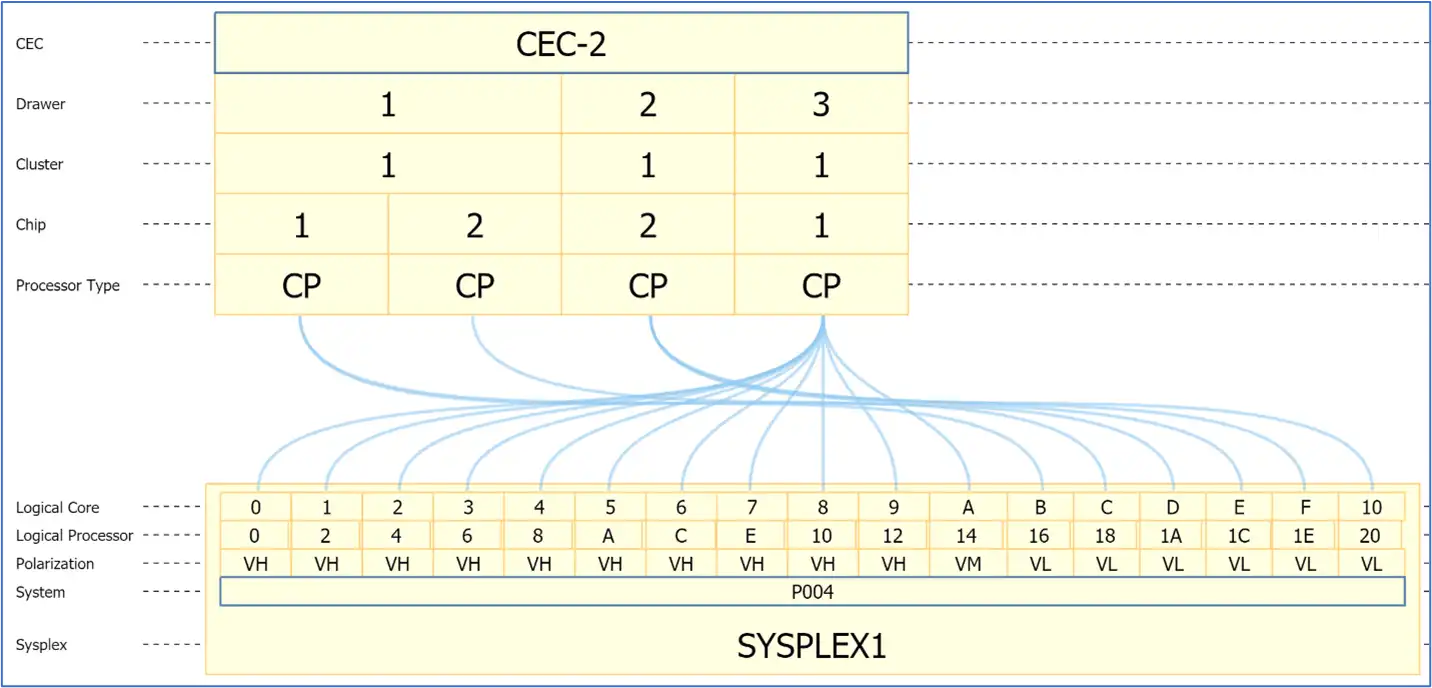

Here is an example of an IntelliMagic Topology view for a single LPAR.

Figure 2: LPAR CP Topology

Notice the number, polarity of the general processors (labeled Processor Type CP), and their location on this CEC.

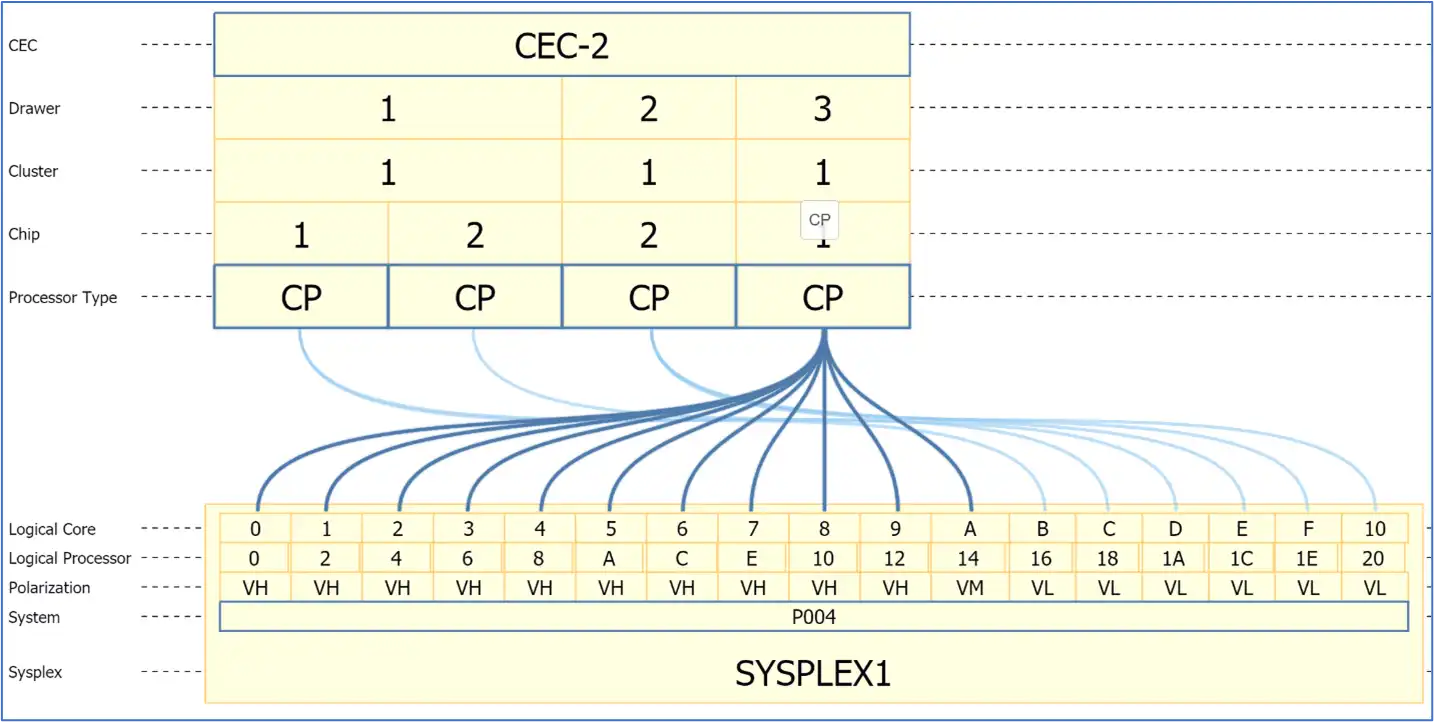

We can also highlight a certain connection or chip and see the relevant logical Processors.

Figure 3: Highlighted Chip

We can clearly see that the Vertical High (VH) processors and the Vertical Medium processor are on the same chip (good). The Vertical Low (VL) processors are spread across other chips, clusters and drawers. When work is dispatched and moved between these processors, it will suffer from cache misses and require many more processor cycles to complete.

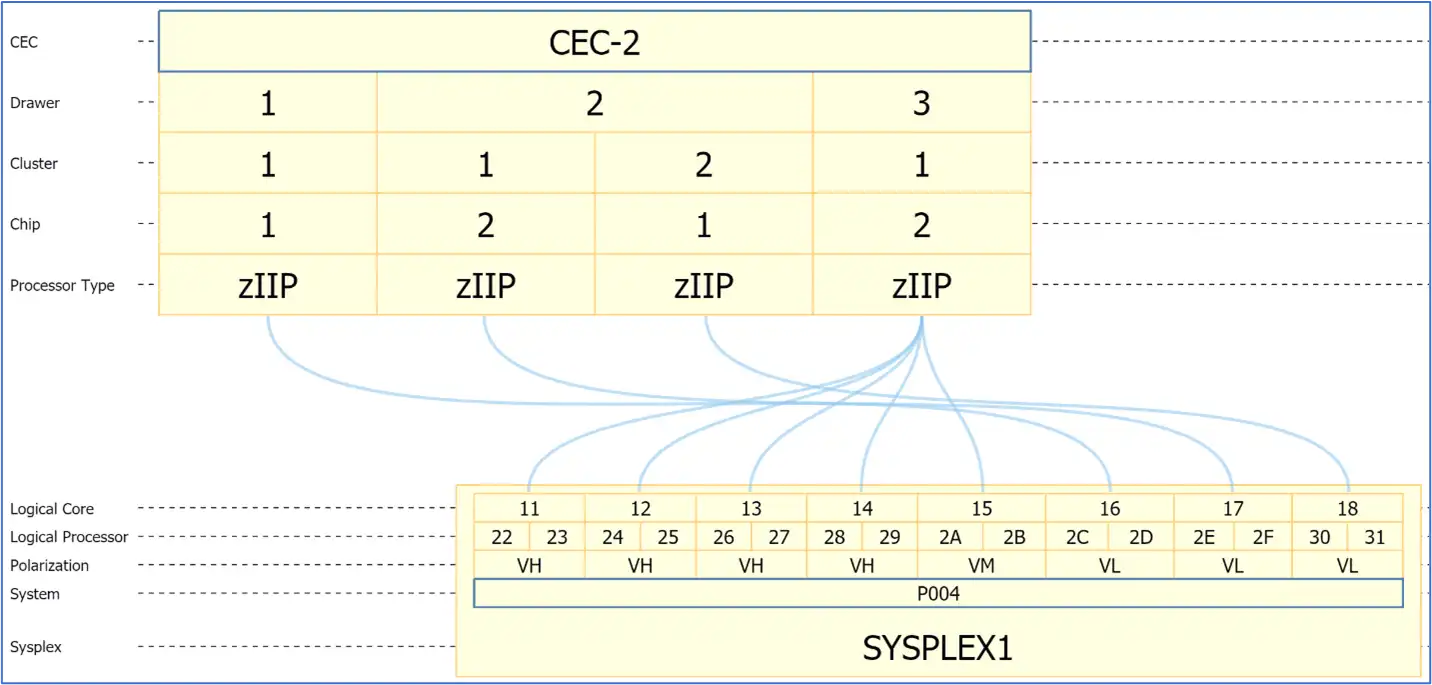

We can also look at the zIIP processor Topology.

Figure 4: LPAR zIIP Topology

The zIIP processors also have a polarity, and we can see here that the Vertical Highs and the Vertical Medium processors are on the same chip. The Vertical Low processors are spread across other chips, clusters and drawers.

We can also see that this LPAR is using SMT (Simultaneous Multithreading) for the zIIP processors. We have used the term “Logical Core” to refer to the zIIP processor, and “Logical Processor” for each of the two threads. For example: Logical Core 11 has two threads, namely 22 and 23.

Note: When looking at the LPAR topology, it is important to realize that the processor assignments may change frequently. The topology may well be different during the peak day online time frame compared to the evening batch time frame.

Why Is It Necessary To View/Review The LPAR Topology?

We have seen that decisions made during the LPAR configuration process influence the physical processor share that each logical processor has. Work dispatched onto Vertical High processors will not need to share cache with other processors, and this will result in a more efficient cache usage and fewer processor cycles needed to complete the required work. Work running on Vertical Medium or Vertical Low processors may suffer because data may need to be staged to the processor cache.

As you can see, a Topology picture certainly contains a lot of important information, and in this form is easy to understand. It’s important for us at IntelliMagic to make it easier to view and understand complicated performance and configuration data.

Having an optimal processor configuration will result in optimizing processor and cache usage to get more work done with fewer processor cycles.

Job-level CPU Saving Opportunities in an Enterprise Consumption Environment

Analysts involved in leading CPU reduction efforts will have to focus limited staff resources on the top potential savings opportunities. This article focuses on job-level CPU reduction opportunities.

This article's author

Share this blog

You May Also Be Interested In:

What's New with IntelliMagic Vision for z/OS? 2024.2

February 26, 2024 | This month we've introduced changes to the presentation of Db2, CICS, and MQ variables from rates to counts, updates to Key Processor Configuration, and the inclusion of new report sets for CICS Transaction Event Counts.

From Taped Walls to Your PC: z/OS Configuration Made Simple with Topology | IntelliMagic zAcademy

In this webinar, we explore a technique that integrates diverse data sources from z/OS, presenting them in a clear, concise, and interactive visual format.

IntelliMagic Releases Breakthrough Interactive z/OS Subsystem Topology Viewer

November 6, 2023 | With the release of 12.10.0, IntelliMagic Vision has introduced an interactive z/OS Subsystem Topology Viewer, allowing performance analysts to visualize and directly interact with subsystem connections.

Book a Demo or Connect With an Expert

Discuss your technical or sales-related questions with our mainframe experts today

John Ticic

John Ticic